# AT-AWG-4010 シリーズ シリアル・データ・パターン生成による デジタルロジック回路の評価方法

アプリケーションノート

## SERIAL DATA PATTERN GENERATOR

### はじめに

本アプリケーションノートは、AT-AWG-4010 シリーズ任意信号発生器を使って、標準的なロジックゲートや一般的なデジタルシステムのテストと特性評価を行うための信号を発生させる方法について説明しています。AT-AWG-4010 シリーズ任意信号発生器は、マルチレベルのシリアルパターンを、使い易いユーザーインターフェイスにより簡単に発生させることができます。パルスとエッジ・シェイプ（レベル間遷移時間）を組み合わせる機能により、マルチレベルのパルス生成を容易にします。出力電圧最大 12Vpp (50Ω) 24Vpp (High-Z)、オフセット電圧±6V (50Ω) / ±12V (High-Z)、そして最高 300MHz のシンボル・レートのシリアルパターン信号が発生可能なので、販売終了となった Agilent 8110A シリーズの代替としてご使用になれます。

#### 課題：

- デジタル論理ゲートと周辺回路の特性評価

#### 解決策：

- AWG-4012/4014/4018 任意信号発生器

#### 結果：

- 半導体デバイスの信頼性評価・故障解析・開発の効率アップ

- 本装置でのシミュレーションにより、デジタル論理ゲートの特性評価時間短縮

Active Technologies

## AT-AWG-4010 任意信号発生器の主な機能

### 最大 4 つのロジックレベル

各チャンネルに、最大 4 レベルの独立した電圧値を設定し、ロジック「0」と「1」に加えて、スリー（トライ）ステートバッファ、もしくはバスが駆動されていないときの Weak0 信号をエミュレートすることができます。

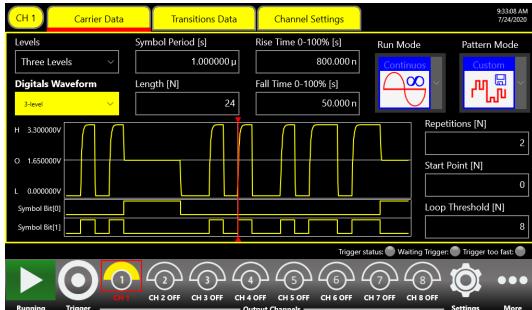

図 1：レベル設定のユーザーインターフェイス

### エッジの定義

各レベル間の遷移時間を、それぞれ個別に設定することができます。この設定により、オーバーシュート等を含む実際の遷移波形に近い信号を出力することができます。垂直分解能 14 ビットと 318MHz のアナログ帯域幅により、忠実な信号を得ることができます。

### 出力電圧

任意信号発生器 AWG-4010 シリーズは、最大 12Vpp (50Ω) /24Vpp (High-Z) の電圧を発生させることができます。さらに、任意の電圧が設定可能なオフセット電圧により ±6V (50Ω) / ±12V (High-Z) の電圧 ウィンドウで出力可能です。

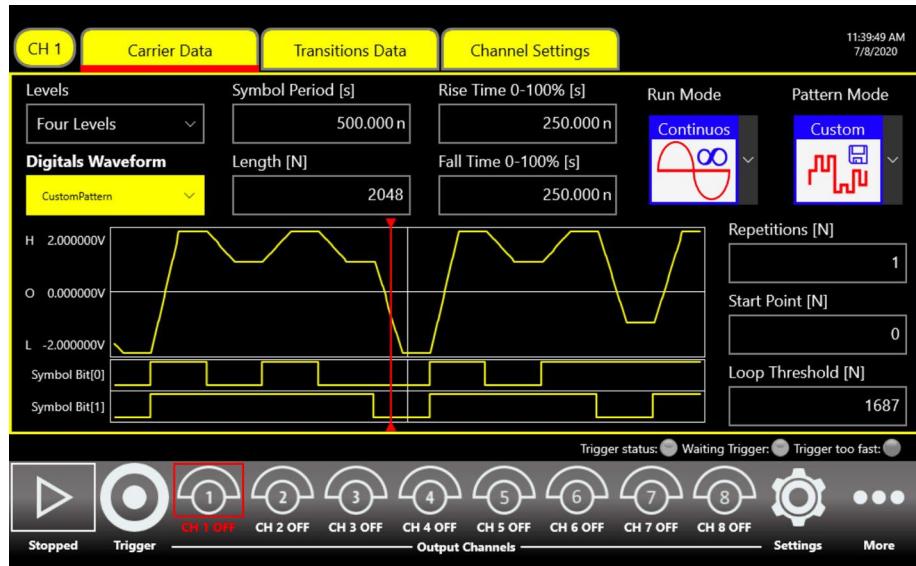

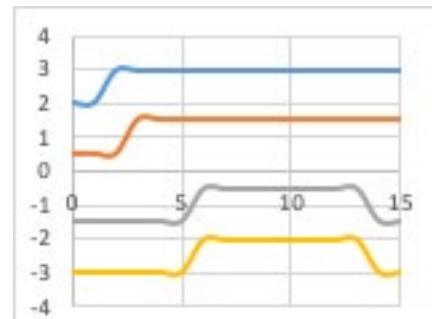

図 2：マルチレベルパターン

### 同期運転（最大 32 チャンネル同期出力）

それぞれのユニットは 8 チャンネルの独立したアナログチャンネルを持ち、最大 4 ユニットまでを同期させることにより 32 チャンネルのシステムを構築することができます。

### 優れた時間解像度

進化したシグナルプロセッサーにより、チャンネル間のスキューは 1ps の時間分解能により設定することができます。

## 生成モード

- Continuous**: Start ボタンが押されると信号出力を開始し、Stop ボタンが押されると出力を停止します。

- Burst** : トリガーが入力されると、設定された回数分のパターンが出力されます。バースト出力が終了すると新たなトリガーの入力を待ちます。

- Modulation** : 出力される信号に AM, FM, PM, FSK, または PSK の変調を加えます。

## 選択可能なヘッダ

メモリー長は最大 2Mbits のパターン長分を搭載していますが、ヘッダ部分のパターンを変化させ、データ部分のパターンを繰り返して出力させることができます。

## 直感的なユーザーインターフェイス

タッチスクリーンやキーボードを使って簡単に波形のプログラムが可能なユーザーインターフェイスを備えています。自動試験装置に組み込む場合、SCPI コマンドを介してパソコンなどで制御させることができます。

図 3：任意信号発生器のユーザーインターフェイス

## 標準的な論理ゲート

標準的な論理ゲートとは、すべてのデジタル回路を構成する基本的な論理ブロックのことを指します。

現在、デジタルアプリケーションの開発は MCU (マイクロコントローラユニット) や PGA (プログラマブルゲートアレイ) などのプログラマブル IC を介して実現されていますが、開発者がプログラマブル IC で直接実現できない機能を必要とする場合、または、アプリケーションがプログラマブル IC に含めるのに十分なほど複雑でない場合、ディスクリートゲートで目的のアプリケーションに対応することができます。

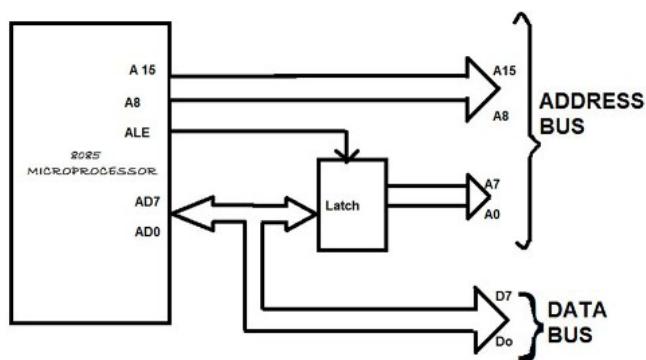

場合によっては、プログラマブルデバイスがサポートできないビットレートを達成するために外部論理ゲートを追加するか、異なる電圧規格の IC 間の通信を可能にするためにレベル変換器を挿入するか、マルチプレクサにより MCU のピンの数を増やす必要があります。

図 4：外部ラッチ回路を使ったアドレス／データバスのデマルチプレクサー

同じ論理機能であっても、TTL、CMOS、BiCMOS など、デバイスには多くの種類があります。

それらの特性評価や試験には、単純な論理回路 (NOT, NAND, NOR など) に対するものから、マルチチャンネル・ラッチやカウンターなど、複雑なものまであり、遷移時間、オーバーシュート、振幅など、それぞれのデバイスの特徴にあわせた信号を出力する必要があります。デジタル信号は、信号の遷移にはわずかな時間がかかり、オーバーシュートの影響を受けるなど、現実的には必ずしも理想的な信号ではなく、各デバイスの実波形に近い、適切な試験信号での評価が必要となります。

これらすべての課題に対して、AWG-4010 シリーズ任意信号発生器は、デジタルパターンを遷移時間、振幅、ノイズ、各種変調などを組み合わせて出力できるので、シリアル信号評価の完璧なソリューションとなります。

次の章では、任意信号発生器を使用してシリアルパターン信号を生成する方法を説明し、例として、典型的なアプリケーションを記述します。

## A. 非同期論理ゲートの伝搬遅延の測定

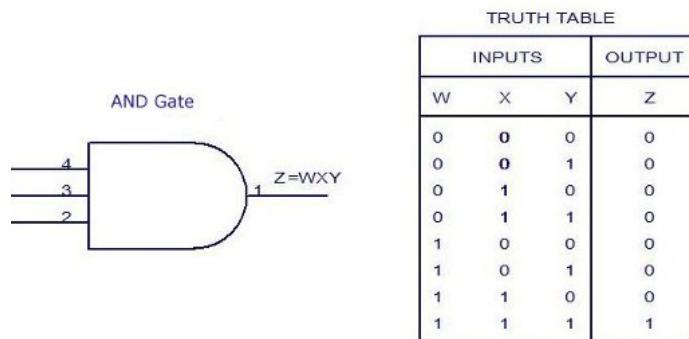

このアプリケーションでは、3 入力の AND ゲートについて説明します。このトピックはすべての論理回路に対して有効です。AND 回路の 3 つの入力は論理的に等価であることが知られていますが、伝搬遅延などのアナログ特性は内部アーキテクチャに依存します。

図 5：3 入力 AND 回路の回路記号と論理表

AT-AWG-4010 シリーズ任意信号発生器を使用して、テスト対象となるゲートの各入力信号のアナログ特性を定義し、電圧レベルと遷移時間をチャネル毎に個別で設定できます。

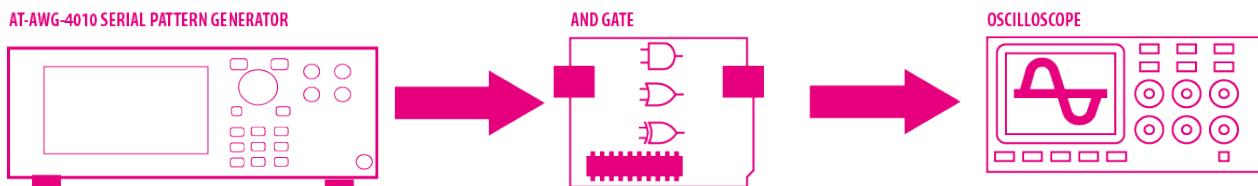

下図はこの試験の構成を示しています：

- 任意信号発生器のチャンネル 1,2,3 は AND 回路の入力に接続されています。

- チャンネル 4 はオシロスコープにリファレンスとして接続されています。

- AND 回路の出力はオシロスコープに接続されています。

- 電源、グランド、その他正常動作に必要となる機器類は簡略化のため省略しています。

図 6：非同期論理ゲートの特性評価用の構成

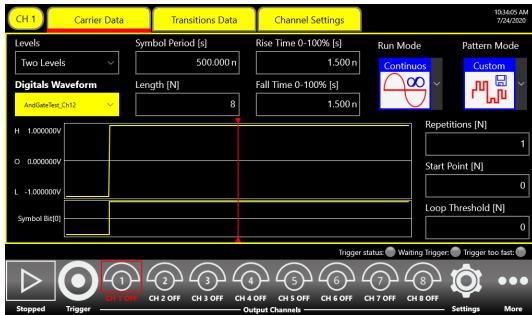

次にソフトウェアインターフェイスを使って任意信号発生器の設定方法を示します。

- “Carrier Data”タブを選択し Levels の設定は”Two Levels”を選択、Symbol Period(ビットレート)を設定し、Pattern Mode は”Custom”を選択します。

図 7 : Carrier Data ページ

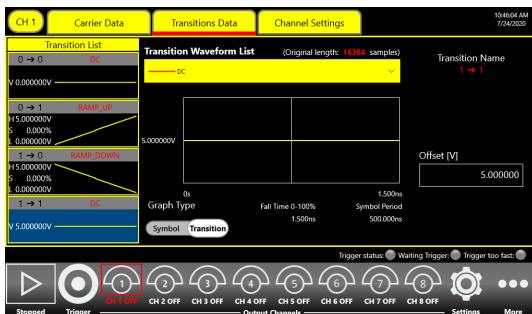

- “Transition Data”タブから各エッジの遷移時間を設定します：このケースでは立ち上がり／立ち下がり時間を 4ns に設定します。次に各遷移の電圧レベルを設定し、レベルを定義します。

図 8 : Transition Data ページ

### 3. パターンを定義します。

Ch1 : 01111111

Ch2 : 01111111

Ch3 : 00011110

Ch4 : 00011110

Ch5-8 : (未使用)

入力 3 の伝搬遅延を評価するため、入力 1 と 2 が同時にハイレベルに遷移して安定してから入力 3 の立ち上がりエッジを実行し、4 つ目のシンボルをハイレベルに保持した後に立ち下がりエッジを実行します。チャンネル 4 はチャンネル 3 と同じ動作をすることから、オシロスコープのリファレンスとして使用します。

図 9: Import ページ

図 10: プログラムパターン

### 4. Run ボタンを押し、結果を観察します

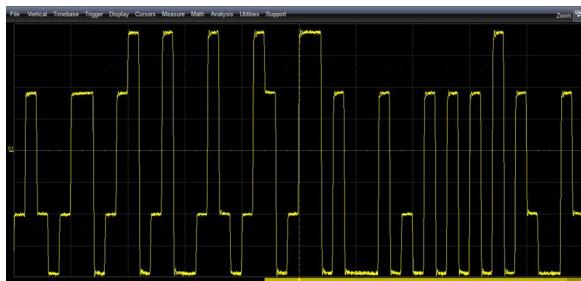

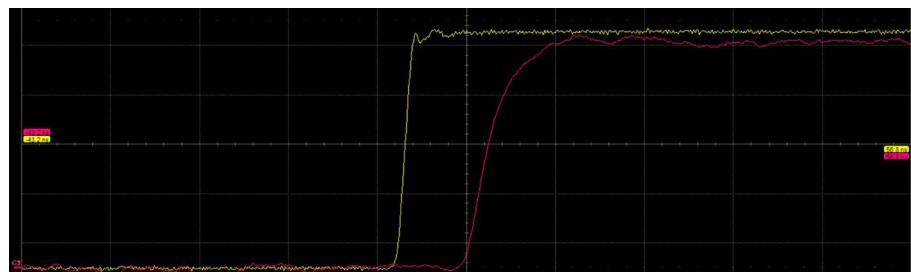

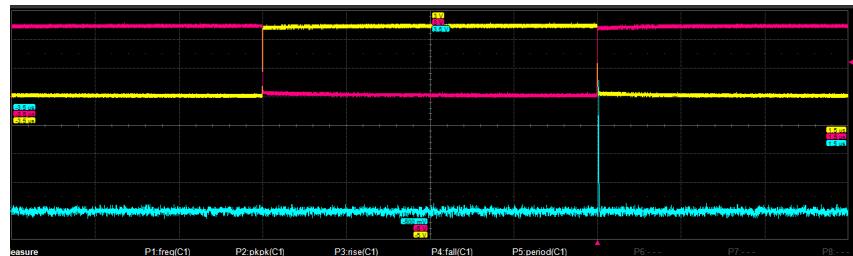

図 11: テスト結果のオシロスコープ画面

上図のオシロスコープ画面では、論理ゲートの出力とチャンネル 4 の間に遅延が生じていることが確認できます。

*Note:* ケーブルによる遅延を補正するため、チャンネル 4 の初期遅延を補正することができます。この設定は、入力 3 の入力から出力への伝搬遅延の特性をより正確に測定するのに有効です。パターンを変更することにより、他の入力の初期遅延も確認することができます。

## B. 非同期論理ゲートにおける同時スイッチによる影響

非同期論理回路を使用して、2つ以上の入力を同時に切り替える場合の論理回路の動作を評価することが重要な場合があります。前述の試験構成で入力2がローレベルの間に入力1をハイレベルにした場合、何が起きるかをテストしてみます。

まず、次のテストパターンをロードします。

Ch 1 : 11000011

Ch 2 : 0111100

Ch 3 : 11111111

Ch 4 – 8 : (未使用)

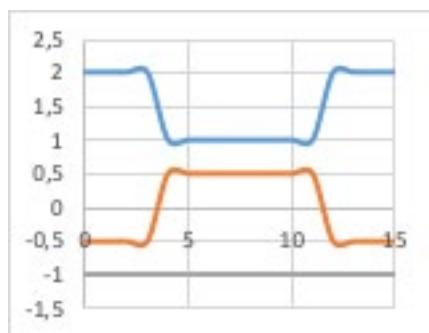

図 12：プログラムパターン

論理的には出力は常に”0”のはずですが、テストで用いられた論理ゲートの内部構造や入力信号のエッジによっては、出力にスパイクが生じることがあります。下図において、出力は常に 0 であるべきところ、入力の切り替え時点(約 7.5 ns)で 2つのスパイクを確認することができます。

図 13：テスト結果のオシロスコープ画面

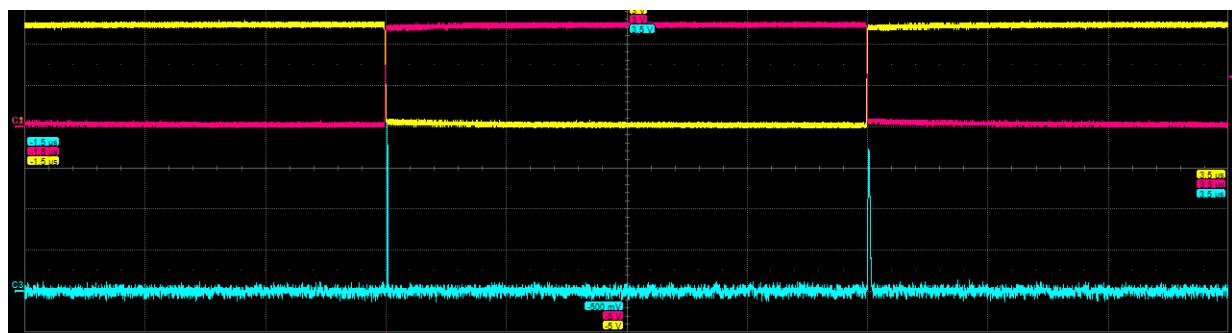

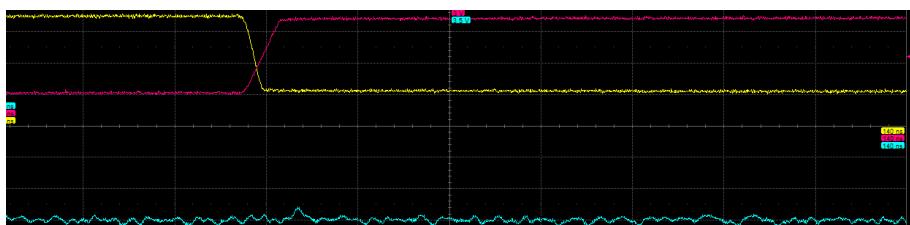

以下は、立ち上がり/立ち下がり時間とチャネル間のスキューを変化させて得られた、オシロスコープのスクリーンショットです。

- ・チャンネル 1-2 間スキュー : 2ns

- ・立ち上がり／立ち下がり時間 : 4ns

図 14：テスト結果のオシロスコープ画面

上図のように、出力にスキーを加えた場合、入力 1 がハイレベルに切り替わった時点でスパイクが発生していることが確認できます。

- ・チャンネル 1-2 間スキー：0

- ・Ch1 立ち上がり時間：7ns

- ・Ch1 立ち下がり時間：4ns

- ・Ch2 立ち上がり時間：7ns

- ・Ch2 立ち下がり時間：4ns

図 15：テスト結果のオシロスコープ画面

上図のように、スキーーや立ち上がり／立ち下がり時間の設定によって、スパイクが発生していないことが確認できます。

## まとめ

AT-AWG-4010 シリーズ任意信号発生器は、デジタルデバイスの特性評価で最も複雑なアプリケーションに対処するための最適なソリューションを提供します。

多チャンネル出力、広い電圧ウィンドウ、任意パターンおよび変調パターン出力は、エンジニアがテスト対象のデバイスを十分に評価するのに便利な機能です。使いやすいユーザーインターフェイスにより、複雑な波形のセットアップも、簡単に素早く行うことができます。

※ 製品を廃棄する場合には、地方自治体の条例・規則に従って廃棄してください。

※ 社名、商品名等は各社の商標または登録商標です。

●製品改良等により、外観および性能の一部を予告なく変更することがあります。

●お問い合わせは、下記当社営業部および営業所または取次店へお問い合わせください。

●価格は変更の可能性があります。ご注文の際にはご確認を頂けますようお願い申し上げます。

**IWATSU**

岩崎通信機株式会社

技術的なお問い合わせ フリーダイヤル：

**0120-102-389** E-mail:[info-tme@iwatsu.co.jp](mailto:info-tme@iwatsu.co.jp)

受付時間 土日祝日を除く営業日の 9:00 ~ 12:00/13:00 ~ 17:00

T&Mカンパニー T&M営業部 URL: <https://www.iwatsu.co.jp/tme>

■計測 営業課 ☎168-8501 東京都杉並区久我山1-7-41 TEL 03-5370-5474 FAX 03-5370-5492

■アカウント営業課 ☎168-8501 東京都杉並区久我山1-7-41 TEL 03-5370-5474 FAX 03-5370-5492

■国際 営業課 ☎168-8501 東京都杉並区久我山1-7-41 TEL 03-5370-5483 FAX 03-5370-5492

■西日本 営業所 ☎550-0005 大阪府大阪市西区西本町2-3-6山崎ビル1F TEL 06-6535-9200 FAX 06-6535-9215

■中日本 営業所 ☎460-0002 愛知県名古屋市中区丸の内3-7-33(アモンドビル) TEL 052-228-3834 FAX 052-951-3576